## Tunnel contacted MoS<sub>2</sub> transistor makes thinnest polarity-tunable rectifier

With the support by the National Natural Science Foundation of China, a collaborative study by the research group led by Prof. Zhang Zhidong (张志东) and Prof. Han Zheng (韩拯) from the Institute of Metal Research, Chinese Academy of Sciences demonstrates that by intercalating a tunneling layer between few-layered MoS2 and Au electrodes, the hetero-structure shows gate-tunable rectifying behavior, which was published in Nature Communications (2017, 8: 970).

Ever since the first discovery of the carbon flatland, the emerging family of two-dimensional (2D) materials has risen as an always-renewed topic for both fundamental and applied physics. In particular, atomically thin 2D semiconducting materials integrated into van der Waals (vdW) heterostructures have enabled architectures that hold great promise for next generation nanoelectronics. However, applications based on one single 2D material in integrated-circuits (especially as CMOS-type logic devices) are still missing. This is mainly due to the fact that 2D materials are either gapless (such as graphene), or are wide-bandgap semiconductors with unipolar operation (such as state-of-the-art MoS<sub>2</sub> transistors). Therefore, the demonstration of a bipolar device that is shown to be compatible for both diode and transistor operations is highly desired.

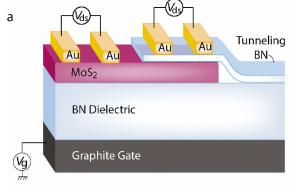

Their group reported a device fabricated by a novel technique further refining the famed micromanipulated vdW 2D layers stacking technique with an added step involving an upside-down reversal of the stack called "reverted vdW stacking". This method enables the integration into vdW heterostructures of atomically thin top layers in an easy and highly reproducible way. When these ultrathin top layers are made of h-BN, this technique enables the integration of high quality and wrinkle-free capping layers that, when electrodes are deposited on top, make possible the routine fabrication Tunnel Contacted Field Effect Transistors (TC-FETs).

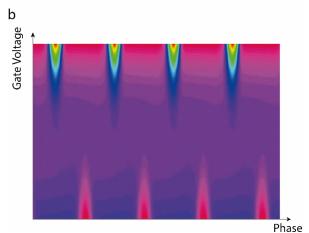

Using the above-mentioned technique, with an MoS<sub>2</sub> conducting channel in the vdW heterostructure, they show that tunnel barriers readily suppress Fermi level pinning and Schottky barriers that occur at metal/  $MoS_2$  contacts (a common pitfall that hinders the application of 2D semiconductors in CMOS logic). The cancellation of band-bending into MoS2 channel leads to homogeneous gate-control of the channel chemical potential across the band-gap edges. It therefore gives rise to the observation of unprecedented features of an ambipolar pn to np diode, which can be reversibly gate-tuned. This technique can be further applied to a broader range of other atomically thin semiconductors and their hetero-structures. It paves the way for future logic applications and high performance switches based on an atomically thin semiconducting channel.

Figure (a) Schematic of MoS<sub>2</sub> TC-FET; (b) rectifying behavior of the TC-FET subjected to an input of sin wave.